- Installation

- User Interface

- Predefined Projects

- Build Configurations

- Project Natures

- Non-top files

- default.build

- Auto-config

- Simulator Log-config

- Emulating compiler invocations

- Multiple .build Files

- Compatibility Modes

- Paths

- Strings

- Comments

- Environment Variables

- Including Other Argument Files

- Build Persistence

- All Build Directives

- SystemVerilog OVM or UVM Library Compilation

- Xilinx Libraries Compilation

- Intel(Altera) Quartus Libraries Compilation

- Questa Libraries Compilation

- Use of External Programs

- Compile Checks

- Quick Fix Proposals

- Content Assist (Autocomplete)

- Hyperlinks

- Show Usages

- Show Readers or Writers

- Show Call Hierarchy

- Show Type Hierarchy

- Show Constraints

- Show Instances

- Peek Exploration

- Refactoring

- Override Functions

- Generate Setters and Getters

- Code Factory

- Code Formatting

- Breadcrumb Navigation Bar

- Diagrams

- Syntax Coloring

- Tooltips

- Workspace Symbols

- > Views

- Quick Search in Views

- Content Filters

- Macros Support

- Inactive Generates Code Highlight

- Database Out of Sync Notification

- External Tools Integration

- UVM Support

- Scripts

- Custom Scripts

- SCM Checkout Hook

- Memory Monitor

- Application Notes

- Handy VS Code Documentation Pointers

- What is New?

- How to Report an Issue?

- Legal Notices

- Third Party Licenses

- Q & A

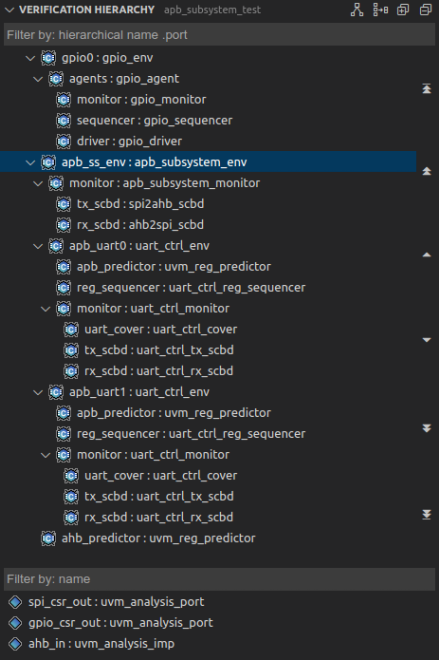

The Verification Hierarchy View presents the UVM object instance tree. An UVM object instance is a class member of an UVM based type that is created using an UVM factory create call.

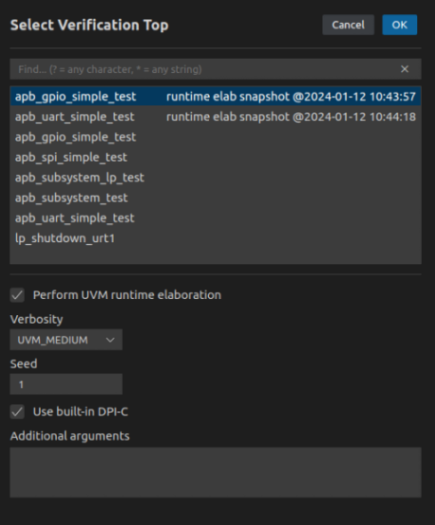

To open the Verification Hierarchy view use the DVT: Focus on Verification View command. To populate the view, use the DVT: Select Verification Hierarchy Top command or the button in the view header.

For the selected UVM test, you have the option to view a statically elaborated hierarchy or perform a runtime elaboration in order to view testbench structures accurately reflecting the configuration at start of simulation.

You can also position the editor cursor on the name of an UVM based class and use the command DVT: Show Verification Hierarchy. The Verification Hierarchy View opens with the chosen element set as the top of the hierarchy.

Scroll through the tree of instances using:

the mouse scroll wheel

the Up arrow, Down arrow, PgUp, PgDn keys

the vertical button bar on the right side of the tree

go to top of tree

go to top of tree up one page

up one page up one element

up one element down one element

down one element down one page

down one page go to bottom of tree

go to bottom of tree

Double-click an instance to go to its UVM factory create call.

Right-click an instance to:

Show Diagram Generate the UVM Component Diagram of the selected instance. More details here.

Copy Hierarchy Path Copy the hierarchical path of the selected instance to clipboard.

Double-click a port to go to its declaration.

Click an instance to see its ports in the lower panel. Right-click a port to copy its hierarchical path to clipboard ( Copy Hierarchy Path ).

You can use the filters to locate a specific instance or port. More details here.