Verissimo SystemVerilog Linter is a coding guideline and verification methodology compliance checker that enables engineers to perform a thorough audit of their design and verification code.

Improves design and verification code quality and reliability.

Prevents incorrect functionality and performance issues.

Automates coding guidelines checking, including UVM Compliance.

Simplifies code maintenance.

Identifies dead code and copy & paste code.

Accelerates language and methodology learning.

Ensures best coding practices are followed.

Speeds up bugfixing.

SystemVerilog provides powerful constructs and a high level of programming flexibility. Its capabilities meet today's complex design and verification requirements, but at the same time introduce new challenges in code development. For example, the ability to implement the same functionality in multiple ways may impact the simulation performance or lead to unexpected behavior.

A SystemVerilog compiler checks whether the source code follows the IEEE 1800 standard rules and as such, it flags only language-specific syntactic and semantic errors. However, the absence of compilation errors does not give any indication of code reliability and maintainability. Nor does it imply that best coding practices have been implemented and compliance with the recommended methodologies like UVM has been met.

Verissimo SystemVerilog Linter enables engineers enforce specific group or corporate coding guidelines to ensure consistency and best practices in code developing.

Features

- Comprehensive library of both generic SystemVerilog and Universal Verification Methodology (UVM) built-in checks.

- Checks for suspicious language usage such as non-standard syntax, problematic delta cycle usage, and prohibited system calls.

- Checks for semantic issues that are not caught by a SystemVerilog compiler, for example, an overridden non-virtual method, which will likely result in unexpected behavior.

- Checks for performance issues like passing arrays by reference to avoid useless copies.

- Checks for dead code, that is for unused code elements such as variables that are never read or written, or functions that are never called.

- Checks for Copy & Paste code duplication.

- Checks for improper styling such as confusing declaration order and naming conventions.

- Checks for verification methodology violations such as inappropriate object creation, missing calls, or constructs that should be avoided.

- Customizable check parameters.

- API for creating new custom checks.

- Ability to create and execute custom rule sets by selecting from available built-in checks.

- Ability to specify per check severity.

- Waivers for filtering exceptions and irrelevant failures.

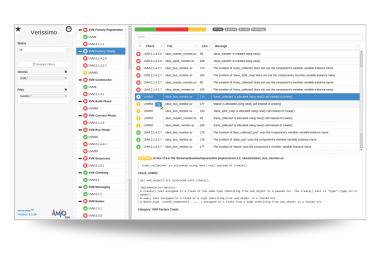

- HTML report with advanced searching and filtering capabilities, bookmarking and monitoring features, including a dashboard that summarizes linting results.

- Support for Batch or GUI mode execution.

- Integration with the DVT IDE (GUI mode, in Eclipse or VS Code)

- Ability to automatically correct violations

6 reasons to choose Verissimo

- Improve design and verification code quality and reliability.

- Prevent incorrect functionality and performance issues.

- Enforce best coding practices.

- Reduce source code maintenance costs.

- Ensure consistency in code developing at the team or company level.

- Create, customize, and implement group or corporate-specific rules.